Transistor de efecto de campo metal-óxido-semiconductor

El transistor de efecto de campo metal-óxido-semiconductor o MOSFET (en inglés metal-oxide-semiconductor field-effect transistor) es un transistor utilizado para amplificar o conmutar señales electrónicas. Es el transistor más utilizado en la industria microelectrónica, ya sea en circuitos analógicos o digitales, aunque el transistor de unión bipolar fue mucho más popular en otro tiempo. Prácticamente la totalidad de los microprocesadores comerciales están basados en transistores MOSFET.

| MOSFET (Transistor de efecto campo MOS) | ||

|---|---|---|

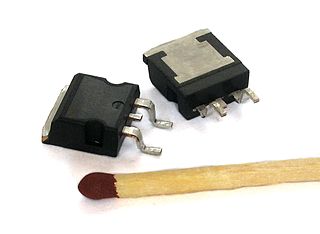

Transistores MOSFET en encapsulado D2PAK. Cada uno maneja 30 A de corriente y 120 V de tensión. Un fósforo o cerilla aparece al lado para efectos de comparación. | ||

| Tipo | Semiconductor | |

| Principio de funcionamiento | Efecto de campo | |

| Invención | Dawon Kahng y Martin Atalla (1960) | |

| Símbolo electrónico | ||

| ||

| Terminales | Puerta (G), Drenaje (D) y Fuente (S). A veces se incluye un cuarto terminal de Sustrato (B). | |

El MOSFET es un dispositivo de cuatro terminales llamados fuente (S), drenador (D), puerta (G) y sustrato (B). Sin embargo, el sustrato generalmente está conectado internamente al terminal de fuente y por este motivo se pueden encontrar dispositivos MOSFET de tres terminales.

El término 'metal' en el nombre MOSFET es actualmente incorrecto ya que el aluminio que fue el material de la puerta hasta mediados de 1970 fue sustituido por el silicio policristalino debido a su capacidad de formar puertas auto-alineadas. Las puertas metálicas están volviendo a ganar popularidad, dada la dificultad de incrementar la velocidad de operación de los transistores sin utilizar componentes metálicos en la puerta. De manera similar, el 'óxido' utilizado como aislante en la puerta también se ha reemplazado por otros materiales con el propósito de obtener canales fuertes con la aplicación de tensiones más pequeñas.

Un transistor de efecto de campo de puerta aislada o IGFET (insulated-gate field-effect transistor) es un término relacionado que es equivalente a un MOSFET. El término IGFET es más inclusivo, ya que muchos transistores MOSFET utilizan una puerta que no es metálica, y un aislante de puerta que no es un óxido. Otro dispositivo relacionado es el MISFET, que es un transistor de efecto de campo metal-aislante-semiconductor (metal-insulator-semiconductor field-effect transistor).

Historia editar

El físico austro-húngaro Julius Edgar Lilienfeld solicitó en Canadá en el año 1925[1] una patente para "un método y un aparato para controlar corrientes eléctricas" y que se considera el antecesor de los actuales transistores de efecto campo. Lilienfeld también solicitó patentes en los Estados Unidos en los años 1926[2] y 1928[3][4] pero no publicó artículo alguno de investigación sobre sus dispositivos, ni sus patentes citan algún ejemplo específico de un prototipo de trabajo. Debido a que la producción de materiales semiconductores de alta calidad aún no estaba disponible por entonces, las ideas de Lilienfeld sobre amplificadores de estado sólido no encontraron un uso práctico en los años 1920 y 1930.[5]

En 1948, fue patentado el primer transistor de contacto de punto por el equipo de los estadounidenses Walter Houser Brattain y John Bardeen[6] y de manera independiente, por los alemanes Herbert Mataré y Heinrich Welker, mientras trabajaban en la Compagnie des Freins et Signaux, una subsidiaria francesa de la estadounidense Westinghouse, pero al darse cuenta estos últimos de que los científicos de Laboratorios Bell ya habían inventado el transistor antes que ellos, la empresa se apresuró a poner en producción su dispositivo llamado "transistron" para su uso en la red telefónica de Francia.[7]

En 1951, Wiliam Shockley solicitó la primera patente de un transistor de efecto de campo,[8] tal como se declaró en ese documento, en el que se mencionó la estructura que ahora posee. Al año siguiente, George Clement Dacey e Ian Ross, de los Laboratorios Bell, tuvieron éxito al fabricar este dispositivo,[9] cuya nueva patente fue solicitada el día 31 de octubre de 1952[10] El primer transistor MOSFET fue construido por el coreano-estadounidense Dawon Kahng y el egipcio Martin Atalla, ambos ingenieros de los Laboratorios Bell, en 1960.[11][12]

Estructura editar

Con una operación y estructura completamente distintas al transistor bipolar de unión, el transistor MOSFET fue creado al colocar una capa aislante en la superficie de un semiconductor y luego colocando un electrodo metálico de puerta sobre el aislante. Se utilizó silicio cristalino para el semiconductor base, y una capa de dióxido de silicio creada a través de oxidación térmica, como aislante. El MOSFET de silicio no generaba trampas de electrones localizados entre la interfaz, entre el silicio y la capa de óxido nativo, y por este motivo se veía libre de la dispersión y el bloqueo de portadores que limitaba el desempeño de los transistores de efecto de campo anteriores.

Después del desarrollo de cuartos limpios para reducir los niveles de contaminación, y del desarrollo de la fotolitografía así como del proceso planar que permite construir circuitos en muy pocos pasos, el sistema Si-SiO2 (silicio-dióxido de silicio) obtuvo gran importancia debido a su bajo costo de producción por cada circuito, y la facilidad de integración. Adicionalmente, el método de acoplar dos MOSFET complementarios (de canal N y canal P) en un interruptor de estado alto/bajo, conocido como CMOS, implicó que los circuitos digitales disiparan una cantidad muy baja de potencia, excepto cuando son conmutados. Por estos tres factores, los transistores MOSFET se han convertido en el dispositivo utilizado más ampliamente en la construcción de circuitos integrados.

Símbolos de transistores MOSFET editar

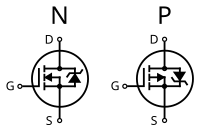

Existen distintos símbolos que se utilizan para representar al transistor MOSFET. El diseño básico consiste en una línea recta para dibujar el canal, con líneas que salen del canal en ángulo recto y luego hacia afuera del dibujo de forma paralela al canal, para indicar la fuente y el drenaje. En algunos casos, se utiliza una línea segmentada en tres partes para el canal del MOSFET de enriquecimiento, y una línea sólida para el canal del MOSFET de empobrecimiento. Otra línea es dibujada en forma paralela al canal para destacar la puerta.

La conexión del sustrato, en los casos donde se muestra, se coloca en la parte central del canal con una flecha que indica si el transistor es PMOS o NMOS. La flecha siempre apunta en la dirección P hacia N, de forma que un NMOS (Canal N en un sustrato P) tiene la flecha apuntando hacia adentro (desde el sustrato hacia el canal). Si el sustrato está conectado internamente a la fuente (como generalmente ocurre en dispositivos discretos) se conecta con una línea en el dibujo entre el sustrato y la fuente. Si el sustrato no se muestra en el dibujo (como generalmente ocurre en el caso de los diseños de circuitos integrados, debido a que se utiliza un sustrato común) se utiliza un símbolo de inversión para identificar los transistores PMOS, y de forma alternativa se puede utilizar una flecha en la fuente de forma similar a como se usa en los transistores bipolares (la flecha hacia afuera para un NMOS y hacia adentro para un PMOS).

En la tabla que seguidamente se muestra se tiene una comparación entre los símbolos de los MOSFET de enriquecimiento y de empobrecimiento, junto con los símbolos para los JFET dibujados con la fuente y el drenaje ordenados de modo que las tensiones más elevadas aparecen en la parte superior del símbolo y la corriente fluye hacia abajo.

Para aquellos símbolos en los que el terminal del sustrato se muestra, aquí se representa conectado internamente al terminal de fuente. Esta es la configuración típica, pero no significa que sea la única configuración importante. En general, el MOSFET es un dispositivo de cuatro terminales, y en los circuitos integrados muchos de los MOSFET comparten una conexión común entre el sustrato, que no está necesariamente conectada a los terminales de la fuente de todos los transistores.

Funcionamiento editar

Existen dos tipos de transistores MOSFET, ambos basados en la estructura MOS. Los primeros son los MOSFET de enriquecimiento, que se basan en la creación de un canal entre el drenador y la fuente, al aplicar una tensión en la puerta. La tensión de la puerta atrae portadores minoritarios hacia el canal, de manera que se forma una región de inversión, es decir, una región con dopado opuesto al que tenía el sustrato originalmente. El término enriquecimiento hace referencia al incremento de la conductividad eléctrica debido a un aumento de la cantidad de portadores de carga en la región correspondiente al canal. El canal puede formarse con un incremento en la concentración de electrones (en un nMOSFET o NMOS), o huecos (en un pMOSFET o PMOS). De este modo un transistor NMOS se construye con un sustrato tipo p y tiene un canal de tipo n, mientras que un transistor PMOS se construye con un sustrato tipo n y tiene un canal de tipo p.

Los MOSFET de empobrecimiento o deplexión tienen un canal conductor en su estado de reposo, que se debe hacer desaparecer mediante la aplicación de la tensión eléctrica en la puerta, lo cual ocasiona una disminución de la cantidad de portadores de carga y una disminución respectiva de la conductividad.

Estructura metal-óxido-semiconductor editar

Una estructura metal-óxido-semiconductor (MOS) tradicional se obtiene haciendo crecer una capa de dióxido de silicio (SiO2) sobre un sustrato de silicio, y luego depositando una capa de metal o silicio policristalino, siendo el segundo el más utilizado. Debido a que el dióxido de silicio es un material dieléctrico, esta estructura equivale a un condensador plano, en donde uno de los electrodos ha sido reemplazado por un semiconductor.

Cuando se aplica un potencial a través de la estructura MOS, se modifica la distribución de cargas en el semiconductor. Si consideramos un semiconductor de tipo p (con una densidad de aceptores NA), p es la densidad de huecos; p = NA en el silicio intrínseco), una tensión positiva VGB aplicada entre la puerta y el sustrato (ver figura) crea una región de agotamiento debido a que los huecos cargados positivamente son repelidos de la interfaz entre el aislante de puerta y el semiconductor. Esto deja expuesta una zona libre de portadores, que está constituida por los iones de los átomos aceptores cargados negativamente (ver Dopaje (semiconductores)). Si VGB es lo suficientemente alto, una alta concentración de portadores de carga negativos formará una región de inversión localizada en una franja delgada contigua a la interfaz entre el semiconductor y el aislante. De manera distinta al MOSFET, en donde la zona de inversión ocasiona que los portadores de carga se establezcan rápidamente a través del drenador y la fuente, en un condensador MOS los electrones se generan mucho más lentamente mediante generación térmica en los centros de generación y recombinación de portadores que están en la región de agotamiento. De forma convencional, la tensión de puerta a la cual la densidad volumétrica de electrones en la región de inversión es la misma que la densidad volumétrica de huecos en el sustrato se llama tensión de umbral.

Esta estructura con un sustrato de tipo p es la base de los transistores nMOSFET, los cuales requieren el dopado local de regiones de tipo n para el drenador y la fuente.

Estructura MOSFET y formación del canal editar

Un transistor de efecto de campo metal-óxido-semiconductor (MOSFET) se basa en controlar la concentración de portadores de carga mediante un condensador MOS existente entre los electrodos del sustrato y la puerta. La puerta está localizada encima del sustrato y aislada de todas las demás regiones del dispositivo por una capa de dieléctrico, que en el caso del MOSFET es un óxido, como el dióxido de silicio. Si se utilizan otros materiales dieléctricos que no sean óxidos, el dispositivo es conocido como un transistor de efecto de campo metal-aislante-semiconductor (MISFET). Comparado con el condensador MOS, el MOSFET incluye dos terminales adicionales (fuente y drenador), cada uno conectado a regiones altamente dopadas que están separadas por la región del sustrato. Estas regiones pueden ser de tipo p o n, pero deben ser ambas del mismo tipo, y del tipo opuesto al del sustrato. La fuente y el drenador (de forma distinta al sustrato) están fuertemente dopadas y en la notación se indica con un signo '+' después del tipo de dopado.

Si el MOSFET es de canal n (NMOS) entonces las regiones de dopado para la fuente y el drenador son regiones 'n+' y el sustrato es una región de tipo 'p'. Si el MOSFET es de canal p (PMOS) entonces las regiones de dopado para la fuente y el drenador son regiones 'p+' y el sustrato es una región de tipo 'n'. El terminal de fuente se denomina así porque es el origen de los portadores de carga (electrones en el canal n, huecos en el canal p) que fluyen a través del canal; de forma similar, el drenador es el punto en el cual los portadores de carga abandonan el canal.

La ocupación de las bandas de energía en un semiconductor está determinada por la posición del nivel de Fermi con respecto a los bordes de las bandas de energía del semiconductor. Como se describe anteriormente, y como se puede apreciar en la figura, cuando se aplica una tensión de puerta suficiente, el borde de la banda de valencia se aleja del nivel de Fermi, y los huecos presentes en el sustrato son repelidos de la puerta. Cuando se polariza todavía más la puerta, el borde de la banda de conducción se acerca al nivel de Fermi en la región cercana a la superficie del semiconductor, y esta región se llena de electrones en una región de inversión o un canal de tipo n originado en la interfaz entre el sustrato tipo p y el óxido. Este canal conductor se extiende entre el drenador y la fuente, y la corriente fluye a través del dispositivo cuando se aplica un potencial entre el drenador y la fuente. Al aumentar la tensión en la puerta, se incrementa la densidad de electrones en la región de inversión y por lo tanto se incrementa el flujo de corriente entre el drenador y la fuente.

Para tensiones de puerta inferiores a la tensión de umbral, el canal no tiene suficientes portadores de carga para formar la zona de inversión, y de esta forma sólo una pequeña corriente de subumbral puede fluir entre el drenador y la fuente.

Cuando se aplica una tensión negativa entre puerta-fuente (positiva entre fuente-puerta) se crea un canal de tipo p en una superficie del sustrato tipo n, de forma análoga al canal n, pero con polaridades opuestas para las cargas y las tensiones. Cuando una tensión menos negativa que la tensión de umbral es aplicada (una tensión negativa para el canal tipo p) el canal desaparece y sólo puede fluir una pequeña corriente de subumbral entre el drenador y la fuente.

Modos de operación editar

El funcionamiento de un transistor MOSFET se puede dividir en tres diferentes regiones de operación, dependiendo de las tensiones en sus terminales. En la presente discusión se utiliza un modelo algebraico que es válido para las tecnologías básicas antiguas, y se incluye aquí con fines didácticos. En los MOSFET modernos se requieren modelos computacionales que exhiben un comportamiento mucho más complejo.

Para un transistor NMOS de enriquecimiento se tienen las siguientes regiones:

Corte editar

- Cuando VGS < Vth

- donde Vth es la tensión de umbral del transistor

- De acuerdo con el modelo básico del transistor, en esta región el dispositivo se encuentra apagado. No hay conducción entre la fuente y el drenador, de modo que el MOSFET se comporta como un interruptor abierto.

- Un modelo más exacto considera el efecto de la energía térmica descrita por la distribución de Boltzmann para las energías de los electrones, en donde se permite que los electrones con alta energía presentes en la fuente ingresen al canal y fluyan hacia el drenador. Esto ocasiona una corriente subumbral, que es una función exponencial de la tensión entre puerta-fuente. La corriente subumbral sigue aproximadamente la siguiente ecuación:

- donde ID0 es la corriente que existe cuando VGS = Vth,

- VT = kT/q es el voltaje térmico,

- n = 1 + CD/COX

- donde CD es la capacidad de la región de agotamiento, y

- COX es la capacidad de la capa de óxido.

Región lineal u óhmica editar

- Cuando VGS > Vth y VDS < ( VGS – Vth )

- Al polarizarse la puerta con una tensión mayor que la tensión de umbral, se crea una región de agotamiento en la región que separa la fuente y el drenador. Si esta tensión crece lo suficiente, aparecerán portadores minoritarios (huecos en PMOS, electrones en NMOS) en la región de agotamiento, que darán lugar a un canal de conducción. El transistor pasa entonces a estado de conducción, de modo que una diferencia de potencial entre drenador y fuente dará lugar a una corriente. El transistor se comporta como una resistencia controlada por la tensión de puerta.

- La corriente que entra por el drenador y sale por la fuente es modelada por medio de la ecuación:

-

- donde es la movilidad efectiva de los portadores de carga,

- es la capacidad del óxido por unidad de área,

- es el ancho de la puerta,

- es la longitud de la puerta.

Saturación o activa editar

- Cuando VGS > Vth y VDS > ( VGS – Vth )

- Cuando la tensión entre drenador y fuente supera cierto límite, el canal de conducción bajo la puerta sufre un estrangulamiento en las cercanías del drenador y desaparece. La corriente que entra por el drenador y sale por la fuente no se interrumpe, ya que es debida al campo eléctrico entre ambos, pero se hace independiente de la diferencia de potencial entre ambos terminales.

- En esta región la corriente de drenador se modela con la siguiente ecuación:

Efectos de segundo orden editar

Estas ecuaciones son un modelo sencillo de funcionamiento de los transistores MOSFET, pero no tienen en cuenta un buen número de efectos de segundo orden, como por ejemplo:

- Saturación de velocidad: La relación entre la tensión de puerta y la corriente de drenador no crece cuadráticamente en transistores de canal corto.

- Efecto cuerpo o efecto sustrato: La tensión entre fuente y sustrato modifica la tensión umbral que da lugar al canal de conducción.

- Modulación de longitud de canal.

Aplicaciones editar

La forma más habitual de emplear transistores MOSFET es en circuitos de tipo CMOS, consistentes en el uso de transistores PMOS y NMOS complementarios. Las aplicaciones de MOSFET discretos más comunes son:

- Resistencia controlada por tensión.

- Circuitos de conmutación de potencia (HEXFET, FREDFET, etc).

- Mezcladores de frecuencia, con MOSFET de doble puerta.

Ventajas con respecto a transistores bipolares editar

La principal aplicación de los MOSFET está en los circuitos integrados PMOS, NMOS y CMOS, debido a las siguientes ventajas de los transistores de efecto de campo con respecto a los transistores bipolares:

- Consumo en modo estático muy bajo.

- Tamaño muy inferior al transistor bipolar (actualmente del orden de media micra).

- Gran capacidad de integración debido a su reducido tamaño.

- Funcionamiento por tensión, son controlados por voltaje por lo que tienen una impedancia de entrada muy alta. La intensidad que circula por la puerta se expresa en nanoamperios.

- Los circuitos digitales realizados con MOSFET no necesitan resistencias, lo que conlleva a un ahorro de superficie.

- La velocidad de conmutación es muy alta, siendo expresada en nanosegundos.

- Cada vez se encuentran más en aplicaciones en los convertidores de alta frecuencias y baja potencia.

Escalamiento del MOSFET editar

Las dimensiones más importantes en un transistor MOSFET son la longitud del canal (L) y el ancho de la puerta (W). En un proceso de fabricación se pueden ajustar estos dos parámetros para modificar el comportamiento eléctrico del dispositivo. La longitud del canal (L) se utiliza además para referirse a la tecnología con la cual fue fabricado el componente electrónico. De esta manera, un transistor fabricado con tecnología de 45 nm es un transistor cuya longitud de canal es igual a 45 nm.

El MOSFET ha sido escalado continuamente para reducir su tamaño por varias razones. El motivo principal es que se pueden poner más transistores en una misma área superficial, aumentando la densidad de integración y la potencia de cálculo de los microprocesadores. Para tener una idea, los primeros transistores tenían longitudes de canal de varios micrómetros, mientras que los dispositivos modernos utilizan tecnologías de apenas decenas de nanómetros. En un microprocesador Core i7 de tercera generación fabricado con tecnología de 22 nm se tienen aproximadamente 1480 millones de transistores.[13]

Los trabajos de Richard Feynman y posteriormente de Robert H. Dennard sobre la teoría de escalamiento fueron la clave para reconocer que la reducción continua del dispositivo era posible. Adicionalmente la industria microelectrónica ha tratado de mantener con vigencia la ley de Moore, una tendencia que indica que la cantidad de transistores en un circuito integrado se duplica cada dos años. Para continuar con esta tendencia, Intel inició un proceso de producción en donde la longitud de la puerta es de 32 nm en el 2009 y continúa reduciendo la escala en el 2011 con procesos de 22 nm. Por otro lado, la industria de semiconductores mantiene un "roadmap", el ITRS,[14] que marca las metas del desarrollo de la tecnología MOSFET.

Razones para el escalamiento del MOSFET editar

Los MOSFET pequeños son deseables por varias razones. El motivo principal para reducir el tamaño de los transistores es que permite incluir cada vez más dispositivos en la misma área de un circuito integrado. Esto resulta en circuitos con la misma funcionalidad en áreas más pequeñas, o bien circuitos con más funcionalidades en la misma área. Debido a que los costos de fabricación para una oblea de semiconductor son relativamente estables, el costo por cada circuito integrado que se produce está relacionado principalmente al número de circuitos que se pueden producir por cada oblea. De esta forma, los circuitos integrados pequeños permiten integrar más circuitos por oblea, reduciendo el precio de cada circuito. De hecho, a lo largo de las últimas tres décadas el número de transistores por cada circuito integrado se ha duplicado cada dos o tres años, cada vez que un nuevo nodo de tecnología es introducido. Por ejemplo el número de MOSFETs en un microprocesador fabricado con una tecnología de 45 nm podría ser el doble que para un microprocesador fabricado con tecnología de 65 nm. Esta duplicación de la densidad de integración de transistores fue observada por Gordon Moore en 1965 y es conocida como la Ley de Moore.[15]

También se espera que los transistores más pequeños conmuten más rápido. Por ejemplo, un enfoque de escalamiento utilizado en el MOSFET requiere que todas las dimensiones sean reducidas de forma proporcional. Las dimensiones principales de un transistor son la longitud, el ancho, y el espesor de la capa de óxido. Cada una de estas dimensiones se escala con un factor de aproximadamente 0.7 por cada nodo. De esta forma, la resistencia del canal del transistor no cambia con el escalamiento, mientras que la capacidad de la puerta se reduce por un factor de 0.7. De esta manera la constante de tiempo del circuito RC también se escala con un factor de 0.7.

Las características anteriores han sido el caso tradicional para las tecnologías antiguas, pero para los transistores MOSFET de las generaciones recientes, la reducción de las dimensiones del transistor no necesariamente implica que la velocidad de los circuitos se incremente, debido a que el retardo debido a las interconexiones se vuelve cada vez más importante.

Dificultades en la reducción de tamaño del MOSFET editar

Históricamente, las dificultades de reducir el tamaño del MOSFET se han asociado con el proceso de fabricación de los dispositivos semiconductores, la necesidad de utilizar tensiones cada vez más bajas, y con bajo desempeño eléctrico, requiriendo el rediseño de los circuitos y la innovación (los MOSFETs pequeños presentan mayor corriente de fuga, e impedancia de salida más baja). Producir MOSFETs con longitudes de canal mucho más pequeñas que un micrómetro es todo un reto, y las dificultades de la fabricación de semiconductores son siempre un factor que limita el avance de la tecnología de circuitos integrados. En los años recientes, el tamaño reducido del MOSFET, más allá de las decenas de nanómetros, ha creado diversos problemas operacionales.

Algunos de los factores que limitan el escalamiento del MOSFET son las siguientes:

- Aumento de la corriente de subumbral

- Aumento en las fugas puerta-óxido

- Aumento en las fugas de las uniones fuente-sustrato y drenador-sustrato

- Reducción de la resistencia de salida

- Reducción de la transconductancia

- Capacitancia de interconexión

- Producción y disipación de calor

- Variaciones en el proceso de fabricación

- Retos en el modelado matemático

Enlaces externos editar

- Animación 3D sobre el MOSFET (vídeo publicado con licencia Creative Commons)

- Wikimedia Commons alberga una categoría multimedia sobre Transistor de efecto de campo metal-óxido-semiconductor.

Referencias editar

- ↑ «Patent 272437 Summary» (en inglés). Canadian Intellectual Property Office. Archivado desde el original el 2 de marzo de 2016. Consultado el 19 de febrero de 2016.

- ↑ «Patent US 1745175: Method and apparatus for controlling electric currents» (en inglés). United States Patent Office. Consultado el 19 de febrero de 2016.

- ↑ «Patent US 1877140: Amplifier for electric currents» (en inglés). United States Patent Office. Consultado el 19 de febrero de 2016.

- ↑ «Patent US 1900018: Device for controlling electric current» (en inglés). United States Patent Office. Consultado el 19 de febrero de 2016.

- ↑ Vardalas, John (mayo de 2003). «Twists and Turns in the Development of the Transistor». Today's Engineer. Archivado desde el original el 2 de marzo de 2016. Consultado el 19 de febrero de 2016.

- ↑ «Patent US2524035: Three-electrode circuit element utilizing semiconductive materials» (en inglés). United States Patent Office. Consultado el 13 de marzo de 2016.

- ↑ «1948: The European Transistor Invention» (en inglés). Computer History Museum. Consultado el 7 de marzo de 2016.

- ↑ «Patent US2744970: Semiconductor signal translating devices» (en inglés). United States Patent Office. Consultado el 13 de marzo de 2016.

- ↑ Robinson, C. Paul (2013). «GEORGE C. (CLEMENT) DACEY». Memorial Tributes (en inglés) (The National Academies Press) 17. doi:10.17226/18477. Consultado el 14 de marzo de 2016.

- ↑ «Patent US2778956: Semiconductor signal translating devices» (en inglés). United States Patent Office. Consultado el 13 de marzo de 2016.

- ↑ «Patent US3102230: Electric field controlled semiconductor device» (en inglés). United States Patent Office. Consultado el 7 de marzo de 2016.

- ↑ «1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated» (en inglés). Computer History Museum. Consultado el 7 de marzo de 2016.

- ↑ Intel Corporation. «Moore's Law: Fun Facts» (en inglés). Consultado el 10 de febrero de 2016.

- ↑ «International Technology Roadmap for Semiconductors». Archivado desde el original el 28 de diciembre de 2015.

- ↑ «1965 – "Moore's Law" Predicts the Future of Integrated Circuits». Computer History Museum.