Ventanas de registro

En ingeniería informática, las ventanas de registro son una característica de algunas arquitecturas de conjuntos de instrucciones para mejorar el rendimiento de las llamadas a procedimientos, una operación muy común. Las ventanas de registro fueron una de las características principales del diseño RISC de Berkeley, que luego se comercializarían con los microprocesadores AMD Am29000, Intel i960, Sun Microsystems SPARC e Intel Itanium.

Resumen editar

La mayoría de los diseños de CPU incluyen una pequeña cantidad de memoria de muy alta velocidad conocida como registro. La CPU utiliza los registros para mantener valores temporales mientras trabaja en cadenas de instrucciones más largas. Se puede agregar un rendimiento considerable a un diseño con más registros. Sin embargo, dado que los registros son una parte visible del conjunto de instrucciones de la CPU, el número no se puede cambiar normalmente después de que se haya lanzado el diseño.

Si bien los registros son casi una solución universal para el rendimiento, tienen un inconveniente. Las diferentes partes de un programa de computadora utilizan sus propios valores temporales y, por lo tanto, compiten por el uso de los registros. Debido a que una buena comprensión de la naturaleza del flujo del programa en tiempo de ejecución es muy difícil, no hay una manera fácil para que el desarrollador sepa de antemano cuántos registros debe usar y cuántos debe dejar de lado para otras partes del programa. En general, se ignoran este tipo de consideraciones, y los desarrolladores, y más probablemente, los compiladores que usan, intentan usar todos los registros visibles para ellos. En el caso de procesadores con muy pocos registros, este es también el único curso de acción razonable.

Implementación editar

Registrar ventanas apuntan a resolver este problema. Dado que cada parte de un programa quiere registros para su propio uso, se proporcionan varios conjuntos de registros para las diferentes partes del programa. Si estos registros fueran visibles, habría más registros sobre los que competir, es decir, deben hacerse invisibles.

Hacer que los registros sean invisibles se puede implementar de manera eficiente; La CPU reconoce el movimiento de una parte del programa a otra durante una llamada de procedimiento. Se logra mediante una de una pequeña cantidad de instrucciones (<i id="mwHw">prólogo</i>) y termina con una de un conjunto similarmente pequeño (<i id="mwIQ">epílogo</i>) . En el diseño de Berkeley, estas llamadas harían que un nuevo conjunto de registros se "intercambiara" en ese punto, o se marcara como "muerto" (o "reutilizable") cuando finalice la llamada.

Aplicación en CPUs editar

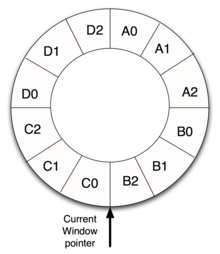

En el diseño del RISC de Berkeley, solo ocho registros de un total de 64 son visibles para los programas. El conjunto completo de registros se conoce como el archivo de registros, y cualquier conjunto particular de ocho como una ventana. El archivo de registros permite que hasta ocho llamadas de procedimiento tengan sus propios conjuntos de registros. Siempre que el programa no llame a cadenas de más de ocho llamadas de profundidad, los registros nunca se deben desbordar, es decir, se guardan en la memoria principal o en la caché, lo que es un proceso lento en comparación con el acceso al registro.

En comparación, la arquitectura SPARC de Sun Microsystems proporciona visibilidad simultánea en cuatro conjuntos de ocho registros cada uno. Tres conjuntos de ocho registros cada uno son "de ventana". Ocho registros (i0 a i7) forman los registros de entrada al nivel de procedimiento actual. Ocho registros (L0 a L7) son locales al nivel de procedimiento actual, y ocho registros (o0 a o7) son las salidas del nivel de procedimiento actual al siguiente nivel llamado. Cuando se llama a un procedimiento, la ventana de registro se desplaza en dieciséis registros, ocultando los registros de entrada antiguos y los registros locales antiguos y haciendo que los registros de salida antiguos los registros de entrada nuevos. Los registros comunes (registros de salida antiguos y nuevos registros de entrada) se utilizan para pasar parámetros. Finalmente, ocho registros (g0 a g7) son visibles globalmente para todos los niveles de procedimiento.

El AMD 29000 mejoró el diseño al permitir que las ventanas sean de tamaño variable, lo que ayuda a la utilización en el caso común donde se necesitan menos de ocho registros para una llamada. También separó los registros en un conjunto global de 64 y 128 adicionales para las ventanas. De manera similar, la arquitectura IA-64 (Itanium) utilizó ventanas de tamaño variable, con 32 registros globales y 96 para las ventanas.

Las ventanas de registro también proporcionan una ruta de actualización fácil. Como los registros adicionales son invisibles para los programas, se pueden agregar ventanas adicionales en cualquier momento. Por ejemplo, el uso de programación orientada a objetos a menudo da como resultado un mayor número de llamadas "más pequeñas", que se pueden acomodar aumentando las ventanas de ocho a dieciséis, por ejemplo. Este fue el enfoque utilizado en SPARC, que ha incluido más ventanas de registro con las nuevas generaciones de la arquitectura. El resultado final es menos operaciones lentas de desborde y relleno de la ventana de registro porque las ventanas de registro se desbordan con menos frecuencia.

Crítica editar

Las ventanas de registro no son la única forma de mejorar el rendimiento del registro. El grupo de la Universidad de Stanford que diseñó el MIPS vio el trabajo de Berkeley y decidió que el problema no era la escasez de registros, sino la mala utilización de los existentes. En su lugar, invirtieron más tiempo en la asignación de registros de su compilador, asegurándose de que sabiamente utilizara el conjunto más grande disponible en MIPS. Esto resultó en una menor complejidad del chip, con la mitad del número total de registros, mientras que ofrece un rendimiento potencialmente mayor en aquellos casos en los que un solo procedimiento podría hacer uso del mayor espacio de registro visible. Al final, con los compiladores modernos, MIPS hace un mejor uso de su espacio de registro incluso durante las llamadas de procedimiento.

Referencias editar

- Frantzen, Mike; Shuey, Mike (2001). "StackGhost: Hardware Facilitado Protección de pila" . Actas del 10º Simposio de Seguridad Usenix . USENIX . páginas. 55–66 . Consultado el 27 de agosto de 2010 .

- Magnusson, Peter (April 1997). «Understanding stacks and registers in the Sparc architecture(s)». Archivado desde el original el 24 de diciembre de 2012. Consultado el 27 de agosto de 2010.

- Mueller, Frank. «setjmp/longjmp». Discutiendo la implementación compleja de Sparc debido a la ventana.