Intel 8255

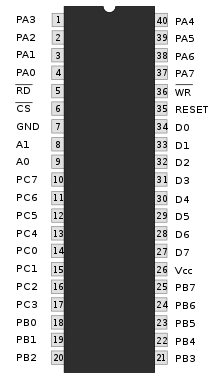

El Intel 8255 (o i8255) Programmable Peripheral Interface (PPI), interfaz programable de periféricos, se utiliza para dar al CPU acceso a puertos de entrada/salida paralela programable. [1] Es un chip controlador de periféricos desarrollado originalmente para el microprocesador Intel 8085,[2] y como tal miembro de una gran lista de chips conocida como la Familia MCS-85. Este chip se utilizó posteriormente con el Intel 8086 y sus sucesores. Fue fabricado (clonado) más tarde por muchos otros fabricantes. Se presenta en un encapsulado DIP de 40 pines, y una versión del 82C55A en encapsulado PLCC (plastic leaded chip carrier) de 44 pines.[3]

Chips similares

editarEl 8255 es muy similar a otros chips como el Motorola 6520 PIA (Peripheral Interface Adapter), el MOS Technology 6522 (Versatile Interface adapter) y el MOS Technology CIA (Complex interface Adapter) todos desarrollados para la familia de CPUs 6502. Otros chips similares son el 2655 Programmable Peripheral Interface para la familia de CPUs Signetics 2650, el 6820 PIO (Peripheral I/O) para el Motorola 6800, el Western Digital WDC 65C21 (un 6520 mejorado), y muchos otros.

Sin embargo, en la mayoría de los casos, la funcionalidad que ofrece el 8255 ya no está implementada mediante el propio chip, sino que está embebida en chips VLSI como una de sus funciones. El chip 8255 todavía se fábrica, y se utiliza junto con un Microcontrolador para expandir sus capacidades de entrada/salida.

Uso

editarEl 8255 fue ampliamente usado no solo en muchos sistemas de microcomputadores/microcontroladores basados en el Zilog Z80, en los ordenadores domésticos Spectravideo SVI-318, Spectravideo SVI-328 y en todas las generaciones MSX, sino también en la tarjeta de sistema del original IBM PC,[4] IBM Personal Computer XT, IBM PCjr, etc, y en equipos compatible IBM PC, junto con numerosos computadores hechos en casa como el N8VEM.

Funcionamiento

editarEl 8255 dispone de un buffer bidireccional triestado de 8 bits que utiliza para interactuar con el bus de datos del sistema. Los datos son transmitidos o recibidos por el buffer tras la ejecución de instrucciones de entrada o salida por la CPU. Las palabras de control y la información de estado también son transferidos a través del buffer.

Bloques funcionales del 8255

editarEl 8255 tiene 24 pines todos de entrada/salida.[5] Estos se dividen en tres puertos de 8 bits (Puerto A, Puerto B, Puerto C).[6] Los puertos A y B se pueden utilizar como puertos de entrada/salida de 8 bits. El puerto C puede ser utilizado como un puerto de entrada/salida de 8 bits o como dos puertos de 4 bits de entrada/salida o para producir las señales de reconocimiento (handshake) para los puertos A y B.

Los tres puertos se agrupan adicionalmente como sigue:

- Grupo A que consiste en el puerto A y la parte superior del puerto C.

- Grupo B que consiste en el puerto B y la parte inferior del puerto C.

Ocho líneas de datos (D0 - D7) están disponibles (con un buffer de datos de 8 bits) para leer/escribir datos en los puertos o control de registro en virtud de la situación de la RD (pin 5) y WR (pin 36), que son señales activas con nivel bajo (0) para operaciones de lectura y escritura respectivamente. Las líneas de dirección A1 y A0 permiten acceder sucesivamente a cualquiera de los puertos o al registro de control como se indica a continuación:

| A1 | A0 | Port selected |

|---|---|---|

| 0 | 0 | puerto A |

| 0 | 1 | puerto B |

| 1 | 0 | puerto C |

| 1 | 1 | registro de control |

La señal de control chip select CS (pin 6) se utiliza para activar el chip 8255. Es una señal activa con nivel bajo, es decir, cuando CS = '0', el 8255 está habilitado. La entrada RESET (pin 35) está conectado a la línea de RESET de la CPU como el 8085, 8086, etc., de modo que cuando el sistema se reinicia, todos los puertos se inicializan como líneas de entrada. Esto se hace para prevenir que el 8255 y/o cualquier periférico conectado a la misma, sean destruidos debido a la falta de coincidencia de los puertos. Como ejemplo, considere un dispositivo de entrada conectado a 8255 en el puerto A. Si de la operación anterior, el puerto A se inicializa como un puerto de salida y, si no se restablece el 8255 antes de usar la configuración actual, entonces hay una posibilidad de daño de cualquiera (el dispositivo de entrada conectado o el 8255 o los dos), ya que ambos, 8255 y el dispositivo conectado, estarán enviando datos.

El registro de control o la lógica de control o la palabra comando de registro (command word register) es un registro de 8 bits que se utiliza para seleccionar los modos de funcionamiento y la designación de entrada/salida de los puertos.[7]

Véase también

editar- IBM PC. Primer computador personal de IBM

- Intel 8086 y 8088. Primeros microprocesadores de la arquitectura x86

- Intel 8284. Generador de reloj

- Intel 8282. Octal Latch

- Intel 8286. Octal Bus Transceiver

- Intel 8288. Controlador de bus

- Intel 8289. Árbitro de bus

- Intel 8237. Controlador programable de DMA

- Intel 8259. Controlador programable de interrupciones (PIC)

- Intel 8253. Temporizador programable de intervalos (PIT)

- Intel 8250 UART. Comunicaciones seriales, RS-232

- Intel 8089. Coprocesador de entrada/salida

Referencias

editar- ↑ Electronics world. Reed Business Pub. 1996. p. 947. Consultado el 10 de diciembre de 2015.

- ↑ Theagarajan, R (1 de enero de 2004). Microprocessor And Its Applications. New Age International. p. 165. ISBN 978-81-224-1040-2. Consultado el 10 de diciembre de 2015.

- ↑ Embedded Systems Programming. Miller Freeman Publications. julio de 1996. p. 256. Consultado el 10 de diciembre de 2015.

- ↑ Jourdain, Robert (1986). Programmer's problem solver for the IBM PC, XT, & AT. Brady Communications Co. p. 3. Consultado el 10 de diciembre de 2015.

- ↑ «Intel 82c55 PPI Datasheet». Intel (en inglés). Consultado el 28 de noviembre de 2015.

- ↑ «PCI 8255A Datasheet». sharpmz.org (en inglés). Archivado desde el original el 26 de septiembre de 2015. Consultado el 28 de noviembre de 2015.

- ↑ Byte. McGraw-Hill. 1981. p. 40. Consultado el 10 de diciembre de 2015.

Bibliografía

editar- Ciriaco García de Celis (1994). «12.2: La interfaz de periféricos 8255». El universo digital del IBM PC, AT y PS/2 (4ª edición). Facultad de Ciencias de Valladolid: Grupo Universitario de Informática.